## Welcome VESA Workshop Taipei, Taiwan 2024

#### **VESA Workshop Agenda**

| Time             | Торіс                                                                                               | Speaker                                                    |

|------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 10:00am          | VESA Overview and Standards Updates,<br>Including DisplayPort v 2.1a and Display<br>Panel Standards | Jim Choate, Compliance Program<br>Manager                  |

| 10:30am          | DisplayPort Link Layer CTS v 2.1                                                                    | Alok Soni, Software Lead, Teledyne<br>LeCroy               |

| 11:00am          | eDP and DP v 2.1 PHY CTS Overview and<br>Updates                                                    | Abhijeet Shinde, Product Manager,<br>Keysight Technologies |

| 11:30am          | DP Alt Mode v 2.1a Overview and CTS<br>Updates                                                      | Mike Micheletti, Product Manager,<br>Teledyne LeCroy       |

| 12:00pm – 1:00pm | Lunch                                                                                               |                                                            |

| 1:00pm           | VESA DisplayHDR Specification Overview and Test                                                     | Robert Yang, Granite River Labs                            |

| 1:40pm           | LRD/Active cable testing and DP 2.1 enhanced connector certification                                | Lexus Lee, Technical Program<br>Manager, Allion Labs       |

| 2:15pm           | UHBR DPTX and DPRX device design challenges                                                         | Jay Lin, Senior Technical Manager,<br>Realtek              |

| 3:00pm – 3:15pm  | Break                                                                                               |                                                            |

| 3:15pm           | VESA Compliance Program                                                                             | Jim Choate, Compliance Program<br>Manager                  |

|                  | Summary, Questions & Answers                                                                        | ividi layei                                                |

| 4:00pm – 4:30pm  | Demo Stations Overview                                                                              |                                                            |

# VESA Overview and Standards Updates

Jim Choate

VESA Compliance Program Manager

10/09/2024

## Agenda

- VESA Overview

- DisplayPort Overview

- VESA Certified DisplayHDR, ClearMR and Adaptive-Sync

- VESA Technology Development Areas

- Summary

## VESA OVERVIEW

#### **About VESA**

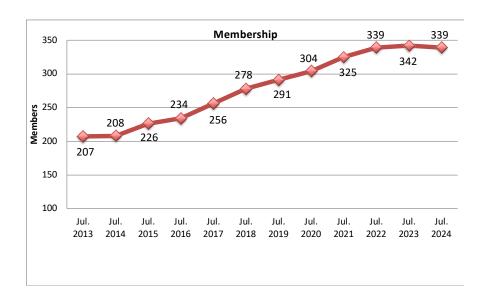

- A growing global industry alliance with nearly 340 members in 2024.

Strong growth in membership over 10 years.

- Mission to develop, promote and support ecosystem of vendors and certified interoperable products for the electronics industry.

- Develops OPEN standards, contribution is open to all companies at all stages of development

## **VESA Membership Growth**

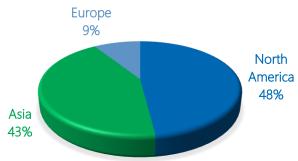

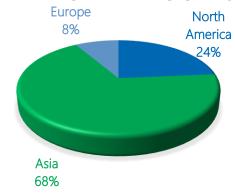

Changes from 2013: Asia + 25%

#### **MEMBERSHIP BY REGION 2024**

## **VESA Standards Enable Many Market Segments...**

Gaming consoles and headsets

Monitors, PCs and laptops

Smartphones and tablets

Automotive

Digital projectors

Digital signage / kiosks

## ...As Well as Many Aspects of Display Technology

- DisplayPort

- Embedded DisplayPort

- DisplayPort Alt Mode (Native DisplayPort over USB-C connector)

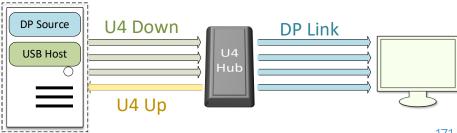

- DisplayPort Tunneling (USB4 and Thunderbolt)

- Automotive Extensions Services (DP AE specification)

- Display Stream Compression (DSC)

- VESA Display Codec for Mobile (VDC-M)

- Standardized Display Performance

Measurement

- DisplayHDR Certification (High Dynamic Range)

- ClearMR Certification

- AdaptiveSync Display Certification

Display Capability Parameters

- DisplayID

- Extended Display Identification Data (EDID)

- Multi-Display Interface (MST)

## **VESA Local Asian Support Capability**

- VESA continues to provide local support to Asia to address growing regional membership needs

- China (Mainland) and Taiwan are the fastest growing areas for VESA's membership.

- **Kellen** is VESA's Representative in Asia

- This partnership provide members with a communication option in their native language. Kellen handles membership related activities including, new membership requests, renewals, event support and translation of VESA member messaging, etc.

- AsiaVESA@kellencompany.com or at +86 10 6580 0670

## DisplayPort ™ Overview

## **DisplayPort Market Penetration**

- DisplayPort adoption continues to grow in 2024

- DisplayPort and DisplayPort Alternate Mode over USB-C

- The common monitor interface for personal computers

- Supported on the USB-C interfaces

- Mandated for USB4 and Thunderbolt

- Automotive integration with DP AE specification

- Mobile phones with USB-C

- Embedded DisplayPort (eDP)

- ~95% penetration in notebook PCs, used in many high-end tablets and now automotive

#### **DisplayPort 2.1a Summary**

- DisplayPort v2.1a was released in December 2023

- Major features added in v2.0/v2.1/v2.1a:

- Added 128b/132b DP channel coding

- Increase in data bandwidth performance (almost 3X) with new link rates up to 20 Gbps/lane

- Panel Replay, similar to PSR (Panel Self Refresh) used for eDP

- DSC support mandated

- Enhanced DP connectors and cables (DP40 and DP80)

- DP PHY specification alignment with USB4 PHY specification

- Updated DP to HDMI v2.1 or higher protocol converter (PCON)

- Corrects errata

- Replaces DP40 cables with DP54 to expand higher rate cable length

- Expanded Tunneling capability

- Updates for DP AE Services specification

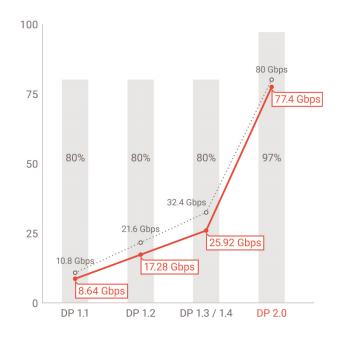

- DisplayPort 2.1a enables up to 3X increase in video bandwidth performance vs DP 1.4

- 3 new data rates added. UHBR10, UHBR13.5 and UHBR20 provides up to 80Gbps link bandwidth for 4 lanes at 20Gbps.

- First standard to support 8K resolution (7680 x 4320) at 60 Hz refresh rate with full-color 4:4:4 resolution, including with 30 bits per pixel (bpp) for HDR-10 support

- Beyond 8K resolutions achieved with maximum link rate to up to 20 Gbps/lane and more efficient 128b/132b channel coding

#### **D**<sup>®</sup> **DisplayPort**™ LUTION OF DISPLAYPORT DATA BANDWIDTH

Max Link Bandwidth (Gbps)

Max Payload Bandwidth (Gbps)

Link Efficiency (Payload Bandwidth/Link Bandwidth)

# DisplayPort 2.1a Resolution Capability (Single Display Examples)

| Port Configuration     | DisplayPort 1.4a           | DisplayPort 2.1a             |

|------------------------|----------------------------|------------------------------|

| No Compression         |                            |                              |

| 4 Lanes, max link rate | 5K (5120x2800)@60fps 24bpp | 10K (10240x4320)@60fps 24bpp |

| 2 Lanes, max link rate | 4K (3840x2160)@60fps 24bpp | 8K (7680x4320)@30fps 30bpp   |

| With Compression (DSC) |                            |                              |

| 4 Lanes, max link rate | 8K (7680x4320)@60fps 30bpp | 16K (15360x8460)@60fps 30bpp |

| 2 Lanes, max link rate | 5K (5120x2800)@60fps 24bpp | 10K (10240x4320)@72fps 30bpp |

#### Notes:

- 2 Lane configuration is common for USB-C DP Alt Mode

- All above modes assume full 4:4:4 color encoding

- 30bpp is required for DisplayHDR operation

#### Key:

- DSC = Display Stream Compression

- fps = frames per second

- bpp = bits per pixel

# VESA Certified DisplayHDR, ClearMR and AdaptiveSync

## **VESA Display Performance Standards**

VESA's display performance work group has been busy since the initial release of the DisplayHDR CTS in 2017.

- VESA Certified DisplayHDR r1.2 update covered by GRL

- VESA Certified AdaptiveSync r1.1

- VESA Certified Clear Motion Ratio (CMR) r1.1

## **DisplayHDR Summary**

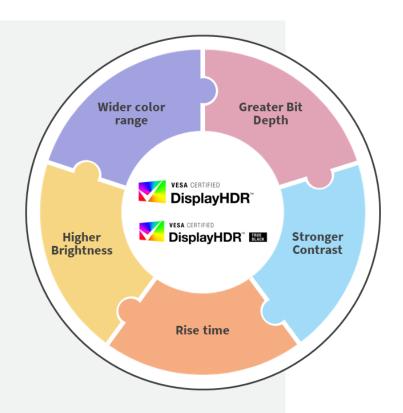

- Industry's first open HDR specification for LCD and emissive (OLED/microLED) displays with a fully transparent testing methodology

- More than 3000 display models certified under logo program to date makes VESA Certified DisplayHDR one of the most successful logo programs in VESA history.

- More details available at <a href="https://displayhdr.org">https://displayhdr.org</a>

VESA Defines New Standard to Help Speed PC Industry Adoption of High Dynamic Range Technology in Laptop and Desktop Monitor Displays

DisplayHDR is industry's first open HDR specification with a fully transparent testing methodology

SAN JOSE, Calif. – December 11, 2017 – The Video Electronics Standards Association (VESA®) today announced it has defined the display industry's first fully open standard specifying high dynamic range (HDR) quality, including luminance, color gamut, bit depth and rise time, through the release of a test specification. The new VESA High-Performance Monitor and Display Compliance Test Specification (DisplayHDR) initially addresses the needs of laptop displays are

## **ClearMR Summary**

- VESA developed motion blur performance compliance test specification for LCD and emissive (OLED/microLED) displays with a new Clear Motion Ratio (CMR) metric and fully transparent testing methodology

- More than 116 display models certified under ClearMR logo program to date

- More details available at <a href="https://www.clearmr.org/">https://www.clearmr.org/</a>

## VESA BRINGS CLARITY TO MOTION BLUR IN DIGITAL DISPLAYS WITH NEW COMPLIANCE TEST SPECIFICATION AND LOGO PROGRAM

ClearMR specification and logo program provide consumers with a true quality metric for grading motion blur performance for LCD and OLED panels, TVs, desktop monitors and embedded displays

BEAVERTON, Ore. – August 22, 2022 – The Video Electronics Standards Association (VESA®) today introduced the ClearMR Compliance Test Specification (ClearMR), an industry standard and logo program that provides a new quality metric for grading motion blur in digital displays. ClearMR is applicable to both LCD and emissive display products, including display panels, TVs, monitors, and computers with embedded displays, such as all-in-ones, laptops, notebooks and tablets. The new metric Clear Motion Ratio (CMR), as

## **VESA Adaptive-Sync Display Summary**

- Industry's first publicly open standard for front-of-screen performance of variable refresh rate displays.

- More details available at <a href="https://www.adaptivesync.org/">https://www.adaptivesync.org/</a>

#### VESA UPDATES ADAPTIVE-SYNC DISPLAY STANDARD WITH NEW DUAL-MODE SUPPORT

#### |German|

VESA Certified AdaptiveSync Dual Mode logo offered for certified displays capable of higher refresh rates when operated in a lower-thanmaximum resolution mode

BEAVERTON, Ore. – January 3, 2024 – The Video Electronics Standards Association (VESA®) today announced that it has published an update to its Adaptive-Sync Display Compliance Test Specification (Adaptive-Sync Display CTS), which is the first publicly open standard for front-of-screen performance of variable refresh rate displays. Adaptive-Sync Display version 1.1a provides updated testing procedures and logo support for an emerging category of displays that can operate at different maximum refresh rates when resolution is reduced. This optional "Dual Mode" testing and logo support allows display OEMs with qualifying hardware to certify their products at two different sets of resolution and refresh rate (for example, 4K/144Hz and 1080p/280Hz).

# DP2.1 Compliance Tests

Name: Alok K. Soni

Company: Teledyne LeCroy

Date: 10/09/2024 (09-Oct-2024)

#### **VESA Approved DP2.1 Compliance Tests Coverage:**

| Source Device Tests:                    |                       |

|-----------------------------------------|-----------------------|

| AUX and HPD (4.2.1.x)                   | FEC (4.5.1.x)         |

| EDID and DPCD (4.2.2.x)                 | DSC (4.6.1.x)         |

| Link Training (4.3.1.x)                 | EDID and NDID (4.7.x) |

| Link Maintenance (4.3.2.x)              | Adaptive Sync (4.8.x) |

| Video (4.3.3.x, 4.4.1.x and 4.4.2.x)    | LTTPR (4.9.1.x)       |

| Power Management (4.4.3.x)              |                       |

| Audio ( <u>Under Review</u> ) (4.4.4.x) |                       |

#### **VESA Approved DP2.1 Compliance Tests Coverage:**

| Sink Device Tests:                      |                         |

|-----------------------------------------|-------------------------|

| AUX(5.2.1.x)                            | Split SDP (5.4.5.x)     |

| DPCD (5.2.2.x)                          | FEC (5.5.1.x)           |

| Link Training (5.3.1.x)                 | DSC (5.6.x.x)           |

| Link Maintenance (5.3.2.x)              | EDID and NDID (5.7.x)   |

| Video (5.4.1.x and 5.4.2.x)             | Adaptive Sync (5.8.1.x) |

| Power Management (5.4.3.x)              | LTTPR (5.9.1.x)         |

| Audio ( <u>Under Review</u> ) (5.4.4.x) |                         |

#### **VESA Approved DP2.1 Compliance Tests Coverage:**

| LTTPR/Tunnel Device Tests:                       | (Loopback setup tests)                  |

|--------------------------------------------------|-----------------------------------------|

| LTTPR Cap (7.1.1.x)                              | 8b10b Non-LTTPR link Training (7.1.8.x) |

| 8b10b Transparent link Training (7.1.2.x)        | Link Maintenance (7.1.9.x)              |

| 8b10b Non-Transparent link Training (7.1.3.x)    | DSC test for SST and MST (7.1.10.x)     |

| 128b132b Non-Transparent link Training (7.1.4.x) | HDCP test for SST and MST (7.1.11.x)    |

| Symbol Error (7.1.5.x)                           | Split SDP (7.1.12.x)                    |

| 8b10b FEC Error (7.1.6.x)                        |                                         |

| 128b132b FEC Error (7.1.7.x)                     |                                         |

#### VESA Approved SCRs Lists (Post DP-v2.1-Link-CTS-r1.0):

| SCR Name & Status:                                                                 | Change Highlights:                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deprecate test 4.3.2.5,<br>update tests 4.2.1.1, 4.2.1.2<br>and 7.1.1.4 (Approved) | <ul> <li>4.3.2.5 Deprecated (lane count reduction)</li> <li>4.2.1.1 and 4.2.1.2 extra time to retry</li> <li>7.1.1.4 LTTPR expected value change for Reg 0xE and 0x220E</li> </ul>                                                                                                                                                                                                                                                                                              |

| SCR to DP v2.1 Link CTS r1.0_multiple_comments_par t1 (Approved)                   | <ul> <li>4.2.2.13 and 4.2.2.14 for AUX Defer Retry check</li> <li>7.1.4.8, 7.1.4.9 and 7.1.4.10 F0008 value validation.</li> <li>5.4.3.1 and 5.4.3.2 Time extended for check.</li> <li>5.4.3.2 and 5.4.3.2 UHBR version of power management tests</li> <li>5.6.3.7 DSC at max Pixel rate validation at UHBR Rate.</li> <li>4.9.1.22 LTTPR First DPCD read F0000h to F0009h after Long HPD.</li> <li>4.3.3.2 Typo correction and 4.6.1.x DSC source table CTS update.</li> </ul> |

| Phase 7 Audio test update (GMR)                                                    | Audio tests update to include UHBR rate. Test Audio for both DSC and non compressed Video for up to UHBR rate.                                                                                                                                                                                                                                                                                                                                                                  |

#### VESA Approved SCRs Lists (Post DP-v2.1-Link-CTS-r1.0):

| SCR Name & Status:                                                                   | Change Highlights:                                                                      |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| SCR to DP v2.1 Link CTS r1.0_ Display ID ARVR<br>HMD update (TGR)                    | Update/New Test (5.7.1.x and 5.7.2.x) to cover new version for ARVR HMD version.        |

| SCR to DP v2.1 Link CTS r1.0_ Minimum HBlank_size and Vblank Period validation (TGR) | New test 5.7.14.7 to validate Hblank and Vblank for detail timing exposed in EDID/NDID. |

| Many more SCR pending: based on following document comments.                         | https://groups.vesa.org/wg/Test/document/20493                                          |

Q/A

# DisplayPort Electrical Testing Overview

Abhijeet Shinde

Keysight Technologies

10/09/2024

## Agenda

- DP2.1a PHY Updates

- DP2.1a Electrical Compliance Test Requirements

- DP2.1a Transmitter Test

- DP2.1a Receiver Test

- eDP PHY Electrical Conformance Testing

# DP2.1a PHY Updates

#### DP2.1 to DP2.1a Electrical Updates

- No changes in 8b/10b electrical compliance testing

- New DP54 Cable model for UHBR10 and UHBR13.5 Source testing

- Test Limit changes in Source and Sink testing

#### UHBR10

- DPTX TP2

- Total Jitter = 380 mUI

- Data-Dependent Jitter = 160 mUI

- Eye Width = 600 mUI

- Eye Height = 242 mV

#### UHBR13.5

- DPTX TP2

- Eye Height = 185 mV

- DPTX TP3 EQ

- Total Jitter =450 mUI

- Data-Dependent Jitter = 200 mUI

- Eye Width = 540 mUI

- Eye Height = 115 mV

- DPRX TP3 EQ

- Total Jitter =485 mUI

- Data-Dependent Jitter = 240 mUI

- Eye Width = 540 mUI

- Eye Height = 112 mV

#### UHBR20

- DPTX TP2

- Total Jitter =435 mUI

- Data-Dependent Jitter = 200 mUI

- Eye Width = 540 mUI

- Eye Height = 240 mV

- DPTX TP3 EQ

- Total Jitter =455 mUI

- Data-Dependent Jitter = 210 mUI

- Eye Width = 560 mUI

- Eye Height = 100 mV

- DPRX TP3\_EQ

- Data-Dependent Jitter = 255 mUI

- Eye Width = 520 mUI

- Eye Height = 96 mV

#### DP2.1a

#### UHBR10

- DPTX TP2

- Total Jitter = 440 mUI

- Data-Dependent Jitter = 220 mUI

- Eye Width = 550 mUI

- Eye Height = 162 mV

#### UHBR13.5

- DPTX TP2

- Eye Height = 200 mV

- DPTX TP3 EQ

- Total Jitter = 515 mUI

- Data-Dependent Jitter = 245 mUI

- Eye Width = 520 mUI

- Eye Height = 80 mV

- DPRX TP3 EQ

- Total Jitter = 530 mUI

- Data-Dependent Jitter = 260 mUI

- Eye Width = 520 mUI

- Eye Height = 73 mV

#### • UHBR20

- DPTX TP2 EnhDP

- Total Jitter =495 mUI

- Data-Dependent Jitter = 220 mUI

- Eye Width = 530 mUI

- Eye Height = 170 mV

- DPTX TP3\_EQ EnhDP

- Total Jitter = 510 mUI

- Data-Dependent Jitter =242 mUI

- Eye Width = 550 mUI

- Eye Height = 84 mV

- DPRX TP3\_EQ EnhDP

- Data-Dependent Jitter = 265 mUI

- Eye Width = 510 mUI

- Eye Height = 80 mV

DPTX TP2 USB-C

Total Jitter =480 mUI

DPTX TP3EO USB-C

• Total Jitter = 500 mUI

## DP2.1a Electrical Compliance Test Requirement

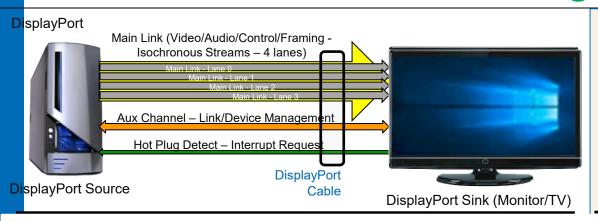

## **DisplayPort Interface**

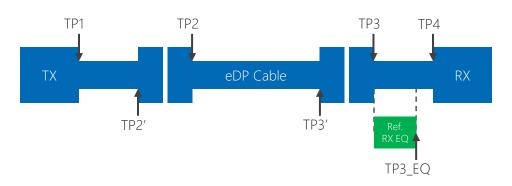

#### Main Link

- Display data transfer

- 4 unidirectional high-speed lanes

- Multiple bitrates supported

#### **AUX Channel**

- Link management

- Test mode control

- 1 bidirectional low-speed lane

#### Hot Plug Detect

- Source detects presence of sink

- Sink notifies of status changes via IRQ

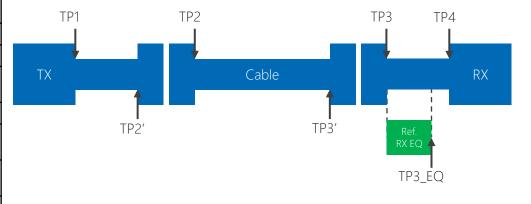

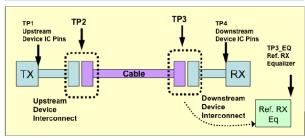

#### **Test Points**

| Test Point | Definition                                                        |

|------------|-------------------------------------------------------------------|

| TP1        | Source transmitter pins.                                          |

| TP2        | Test interface of a TPA, next to mated connection to a DP source. |

| TP2'       | RX JTOL signal injection point for DUTs with plug.                |

| TP2_CTLE   | RX JTOL calibration and test point for DUTs with plug.            |

| TP3        | Test interface of a TPA, next to mated connection to a DP sink.   |

| TP3'       | Signal injection point to a DP sink.                              |

| TP3_EQ     | TP3 using a defined cable model with equalization applied.'       |

| TP3_CTLE   | TP3 using a defined HBR3 cable model with CTLE applied.           |

| TP3_DFE    | TP3 using a defined HBR3 cable model with CTLE and DFE applied.   |

| TP4        | Sink receiver pins.                                               |

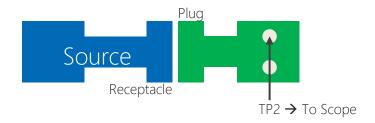

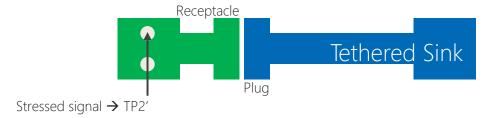

## **Test Point Access Examples**

#### **DPTX Testing**

#### **DPRX Testing**

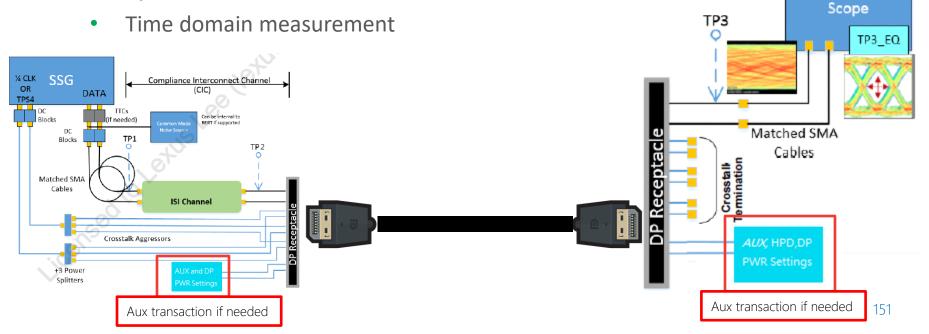

### How to test the PHY layer?

#### Source

- Configure the source to output test patterns with certain drive settings → AUX controller

- Embed worst-case channels, apply equalization on the oscilloscope

- Run measurements

#### Sink

- Generate the stress signal with a pattern generator

- Guide the sink through Link Training → AUX controller

- Read built-in error counter → AUX controller

# DP2.1a Transmitter Test

### **Electrical Transmitter Tests**

| Item | Name                                                                             | Normative/<br>Informative |

|------|----------------------------------------------------------------------------------|---------------------------|

| 3.1  | Eye Diagram Test                                                                 | Normative                 |

| 3.2  | HBR/RBR Non-PE Level Verification Test                                           | Normative                 |

| 3.3  | HBR/RBR PE Level Verification and Maximum Differential Peak-to-Peak Voltage Test | Normative                 |

| 3.4  | HBR3/HBR2 PE Level and Equalization Verification Test                            | Normative                 |

| 3.5  | HBR3/HBR2 V <sub>TX_DIFFp:p_MAX</sub> Test                                       | Normative                 |

| 3.6  | Inter-pair Skew Test                                                             | Informative               |

| 3.7  | Intra-pair Skew Test                                                             | Informative               |

| 3.8  | AC Common Mode Noise Test                                                        | Informative               |

| 3.9  | Non-ISI Jitter Measurement Test                                                  | Normative                 |

| 3.10 | HBR3 TX Differential RL Test                                                     | Informative               |

| 3.11 | TJ/RJ/DJ Measurement Tests                                                       | Normative                 |

| 3.12 | Main-Link Frequency Compliance Test                                              | Normative                 |

| 3.13 | Spread-spectrum Modulation Frequency Test                                        | Normative                 |

| 3.14 | Spread-spectrum Modulation Deviation Test                                        | Normative                 |

| 3.15 | dF/dT Spread-spectrum Deviation High-frequency Variation Test                    | Informative               |

| ltem | Name                                                             | Normative/<br>Informative |

|------|------------------------------------------------------------------|---------------------------|

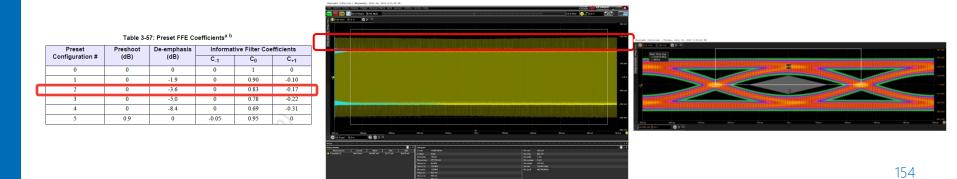

| 4.2  | Preset and CTLE-DFE Declaration                                  | Normative                 |

| 4.3  | UHBR Source Transmitter Equalization                             | Normative                 |

| 4.4  | UHBR Bit Rate                                                    | Normative                 |

| 4.4  | UHBR Unit Interval                                               | Informative               |

| 4.5  | UHBR SSC Down Spread Range, Rate, Phase Deviation, and Slew Rate | Normative                 |

| 4.6  | UHBR Embedded Re-timer Frequency Variation                       | Normative                 |

| 4.7  | UHBR TP2 Eye at 1E-6 BER                                         | Normative                 |

| 4.8  | UHBR TP2 Jitter at 1E-9 BER                                      | Normative                 |

| 4.9  | UHBR AC Common Mode Nosie Test                                   | Informative               |

| 4.10 | UHBR TP3_EQ Eye at 1E-6                                          | Normative                 |

| 4.11 | UHBR TP3_CTLE Jitter at 1E-9                                     | Informative               |

| 4.12 | UHBR Transmitter Return Loss                                     | Informative               |

8b/10b

128b/132b

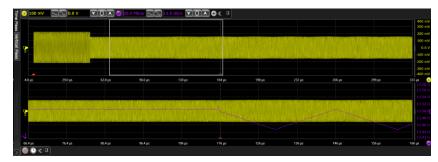

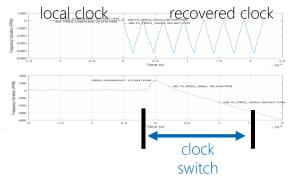

### LTTPR Frequency Variation Test

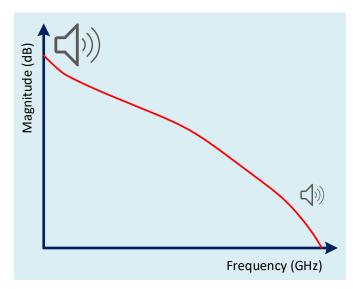

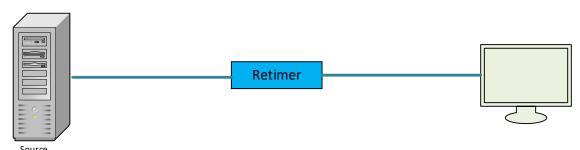

- LTTPRs are needed as total channel loss increases

- with the PHY rate

- Longer channel

- More complex link training

- LTTPR Re-timer Clock Switch Test Mode

- DPCD 0x0010B 0x0010Eh [7] =1

- Initial Test Challenges

- Entering Clock Switch test mode

- Triggering on LTTPR local clock event

### **DP TX testing challenges**

- The test time for DP TX is significant

- DP Source not supporting PHY Test Automation

- DP Source does not transmit the compliance pattern

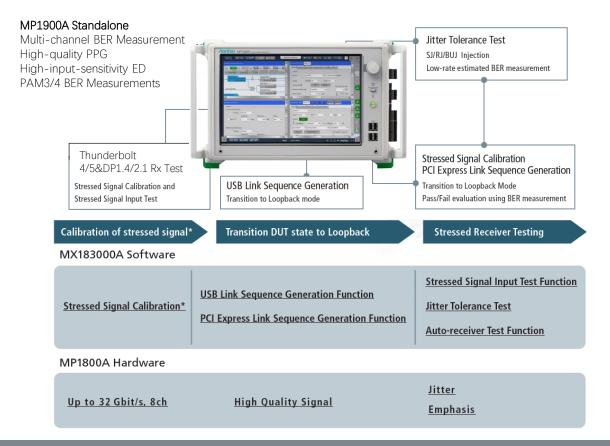

# DP2.1a Receiver Test

### **Electrical Receiver Tests**

| Item | Name                     | Normative/<br>Informative |

|------|--------------------------|---------------------------|

| 5.1  | 8b/10b DP Sink JTOL Test | Normative                 |

| ltem | Name                             | Normative/<br>Informative |

|------|----------------------------------|---------------------------|

| 6.1  | 128b/132b DP UHBR Sink JTOL Test | Normative                 |

| ltem      | Calibration Point | Name                                         |  |

|-----------|-------------------|----------------------------------------------|--|

| 5.1.3.1.1 | TP1-TP3           | HBR3 Jitter Calibration                      |  |

| 5.1.3.1.2 | TP1-TP3           | HBR2 Jitter Calibration                      |  |

| 5.1.3.1.3 | TP1-TP3           | HBR Jitter Calibration                       |  |

| 5.1.3.1.4 | TP2/TP3           | HBR3 Eye Height and Total Jitter Calibration |  |

| 5.1.3.1.4 | TP3               | HBR2 Eye Height and Total Jitter Calibration |  |

| 5.1.3.1.4 | TP3               | HBR Eye Height and Total Jitter Calibration  |  |

| 5.1.3.1.5 | TP1/TP3           | HBR3/HBR2/HBR Crosstalk Calibration          |  |

| 5.1.3.2   | TP2/TP3           | RBR Jitter Calibration                       |  |

| 5.1.3.2   | TP3               | RBR Eye Height Calibration                   |  |

| 5.1.3.2.1 | TP3               | RBR Crosstalk Calibration                    |  |

| ltem        | Calibration Point | Name                                    |

|-------------|-------------------|-----------------------------------------|

| 6.1.3.1.4.1 | TP1               | AC Common-Mode Interference Calibration |

| 6.1.3.1.4.2 | TP1               | Random Jitter Calibration               |

| 6.1.3.1.4.3 | TP1               | Periodic Jitter Calibration             |

| 6.1.3.1.4.4 | TP1               | Total Jitter Calibration                |

| 6.1.3.1.4.5 | TP1               | Eye Height Calibration                  |

| 6.1.3.1.5   | TP3               | Insertion Loss Calibration              |

| 6.1.3.1.6   | TP3               | Eye Diagram Calibration                 |

## **DP RX testing challenges**

- DP Sink does not enable error count registers

- DP RX Preset calibration to be required impacts TE correlation results

- Calibrations take a significant amount of time

- Different setup needs for 8b/10b and 128b/132b

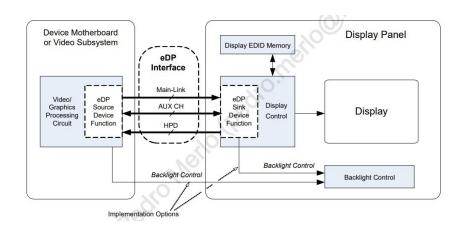

# Embedded DisplayPort

#### eDP

- Standardized features and interoperability guidelines

- Feature set determined by the system integrator

- Current specification is eDP1.5a

- Based on DP1.4a

- No compliance program = Conformance Test!!

### Key Differences eDP1.5 vs DP2.1a 8b/10b rates

#### Required

- DPCD registers for eDP

- Reduced AUX timing

- Enhanced framing

- Fast link training (sink)

- eDP-specific sink noise/jitter budget, reference EQ

#### **Optional**

- Low AUX voltage swing

- Source detection by way of AUX CH

- STREAM\_STATUS\_CHANGED bits support

- GUID registers support

- Fast link training (host)

- Reduced main-link voltage swing level

- EDID

- HPD pin on sink device

#### Recommended

Fewest number of lanes possible

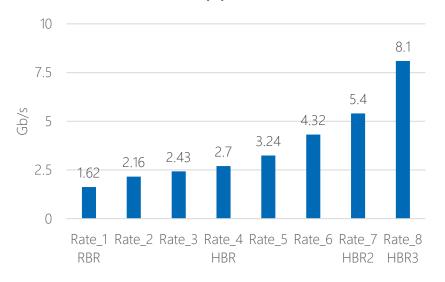

### **Main Link Differences**

- Eight nominal rates

- Custom rates supported

- TP3\_EQ total jitter budget

- BER =  $10^{-9}$

| Test Point | Description                             | I/N         | DJ <sub>MAX</sub> | TJ <sub>MAX</sub> |

|------------|-----------------------------------------|-------------|-------------------|-------------------|

| TP1        | eDPTX package pin Informative 0.1       |             | 0.17 UI           | 0.27 UI           |

| TP2        | Source device eDP cable connector       | Informative | N/A               | N/A               |

| TP3        | Sink device (panel) eDP cable connector | -           | -                 | -                 |

| TP3_EQ     | After reference RX equalizer            | Normative   | 0.41 UI           | 0.50 UI           |

| TP4        | eDPRX package pins                      | Informative | 0.46 UI           | 0.55 UI           |

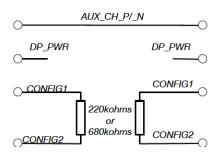

### **AUX Channel Differences**

- No AC-coupling capacitors on Sink device side

- No pull-up/-down resistors

- Why?

- The Sink device does not monitor the common mode voltage on AUX\_CH\_P and AUX\_CH\_N for Source device Hot Plug/Unplug and powered/unpowered detection

### **eDP Electrical Specification**

- Low voltage swing levels

- Framework to apply optional customized voltage swings

- Reduced RX differential voltage sensitivity

- New transfer rates

- Framework to apply jitter specifications to optional customized frequencies

- Same Link Training procedures and voltage swing tables like DP, but with lower signal voltages

### **eDP Transmitter Test**

Test Point/Fixture

| Recommended Source Main-Link TX Electrical Specification |

|----------------------------------------------------------|

| Link Rate                                                |

| Unit Interval                                            |

| Total Jitter                                             |

| Residual ISI                                             |

| Non-ISI                                                  |

| Eye Diagram                                              |

### **eDP** Receiver Test

Test Point/Fixture

| Calibration Point | RX Calibration                |

|-------------------|-------------------------------|

| TP1               | Sinusoidal Jitter Calibration |

| TP1               | Random Jitter Calibration     |

| TP3               | Residual ISI                  |

| TP3               | Eye Diagram                   |

| TP3               | Crosstalk                     |

### eDP2.0 Update

- eDP2.0 draft v0.7 published on Aug 29, 2024

- Supports 128b/132b encoding

- Supports UHBR data rates

- UHBR10, UHBR13.5 and UHBR20

- Leverages worst-case end-to-end link budget from DP2.1a

# Thank You!

# DP Alt-Mode 2.1: A Closer Look

Mike Micheletti

Product Manager

Teledyne LeCroy

10/09/2024

## VESA A Closer Look at DP Alt-Mode 2.1

- Agenda

- DisplayPort 2.1 & Alt Mode Updates

- DP Alt Mode Overview

- Type-C pin configurations

- DPAM 2.1 Version Resolution

- DPAM 2.1 Cable Discovery

- DPAM 2.1 Configuration walk-through

- DPAM 2.1 Compliance Overview

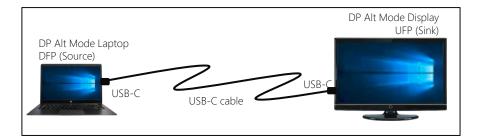

### **VESA** Alternate-Mode Usage Cases

#### Alternate Modes

Goal – Leverage multi-lane Type-C cable to support alternate communications standards over a single physical cable

### Applications

- DisplayPort 1.4 / 2.1

- Thunderbolt™ 3

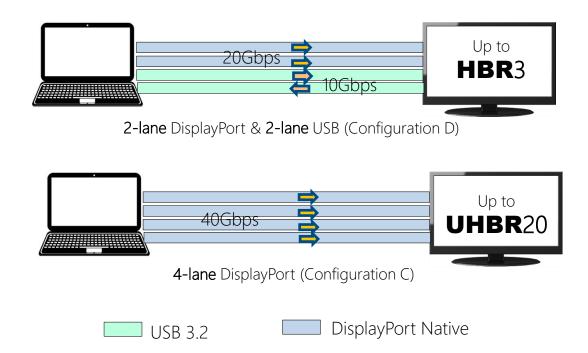

## **VESA** DP Alt-mode Lane Configurations

- Two diff pairs allow up to HBR3 (config: D)

- Four diff pairs allow up to UHBR20 (config: C, E)

### DisplayPort 2.1 & DPAM 2.1 Updates

### VESA What is new in DisplayPort 2.1 Base Spec

- **DP56/DP80** Allows UHBR20 'native' DP cables/connectors

- Active Cables (LTTPR Retimer / LRD)

- USB4 PHY Electrical specification alignment (IR-loss...etc)

- USB4 tunnel changes for UHBR rates

- Revised Link Training DPCD registers as LTTPR "Intra-Hop AUX"

- AUX-less ALPM Power management control over high-speed lines

- CableID allows DP-Tx/DP-Rx to identify DP56 / DP80 cables

- Lots of Clarifications and improvements

## **VESA** What is new in DisplayPort 2.1 Base Spec

- DP56/DP80- Allows UHBR20 'native' DP cables/connectors

- Active Cables (LTTPR Retimer / LRD)

- USB4 PHY Electrical specification alignment (IR-loss...etc)

- USB4 tunnel changes for UHBR rates

- Revised Link Training DPCD registers as LTTPR "Intra-Hop AUX"

- AUX-less ALPM Power management control over high-speed lines

- CableID allows DP-Tx/DP-Rx to identify DP56 / DP80 cables

- Lots of Clarifications and improvements

## **VESA** USB-C DP Alt Mode Signaling

- Main Link: high-bandwidth channel used to transport video/audio

- 1, 2 or 4 Lane Configurations

- Link rates:1.62Gbps 20Gbps

- Aux Channel:

- Bidirectional 1Mbps

- Hot plug signal:

- Connection Detection

- Interrupt mechanism

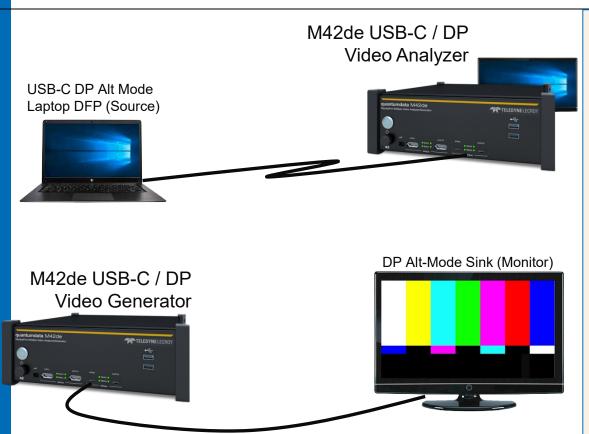

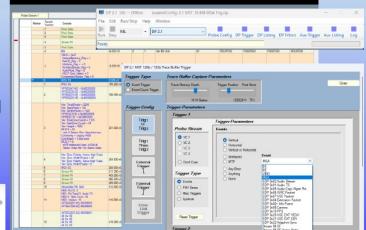

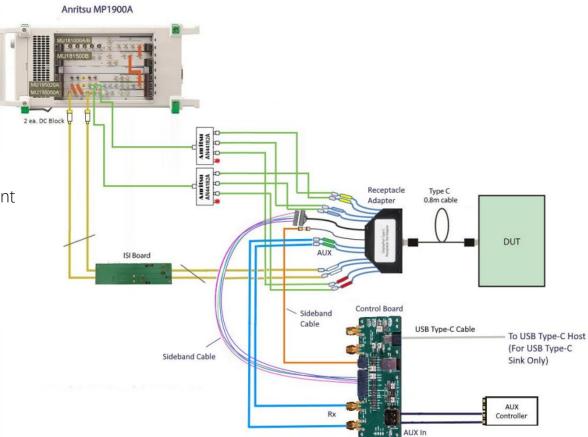

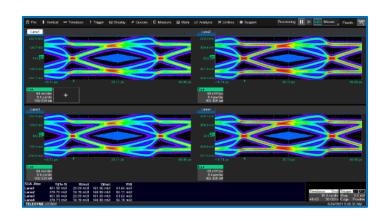

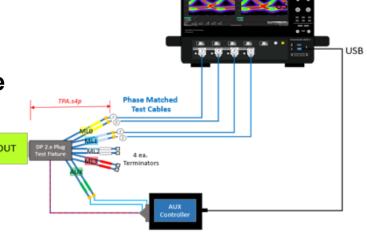

### VESA M42de Supports DP Alt-Mode SRC/SNK Testing

- Protocol Analysis Source Testing

- Sink emulation EDID, DPCD.

- Protocol Analysis Main Link & Aux

- Compliance Testing Link Layer, (including FEC), DŠC, HDCP.

- Video Generation Sink Testing

- Source emulation and Link Training control

- Video Pattern Testing –generation of Display Stream Compression (DSC) Panel Replay and FEC.

- Compliance Testing (Link Layer, FEC, HDCP).

- DP Alt Mode Testing

- Run all VESA source and sink testing through the USB-C DP Alt Mode ports.

## VESA USB-C DP Alt Mode – High Level Overview

#### Key roles for PD/CC messages:

- Discovery DP Alt Mode Capabilities

- Decide which Pin Configuration to use

- DP Sink

- Active cables

- Captures PD and AUX-

- Sequential list of transactions

- Shows full DP-Alt Mode entry flow

- Captures all AUX channel transactions

- Real-time

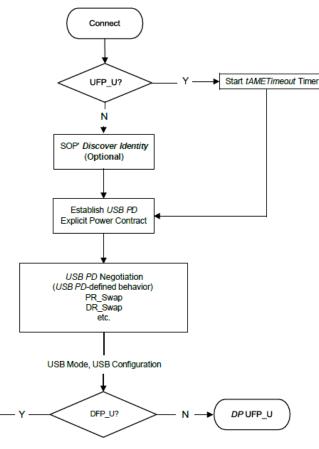

## VESA Getting Ready for DP Alt Mode...

- Initial Type-C State Detection

- Starts tAMETimeout timer

- If Sink does not enter DP Alt Mode within 1

Sec UFP\_U shall present a USB billboard

- Negotiate initial PD Power Contract

- Establish port's data role

- Port assumes the role of either:

- DFP U

- UFP\_U

- Complete any other PD transactions before starting DisplayPort Alt Mode (ie: PR\_Swap)

DP DFP U

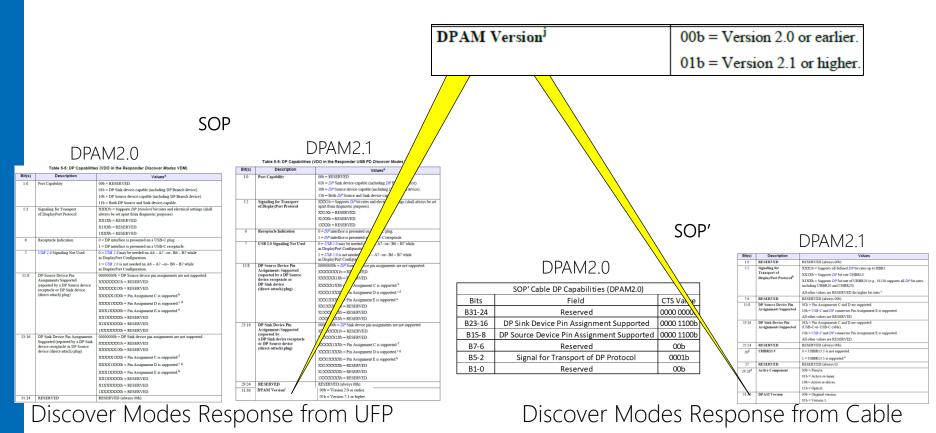

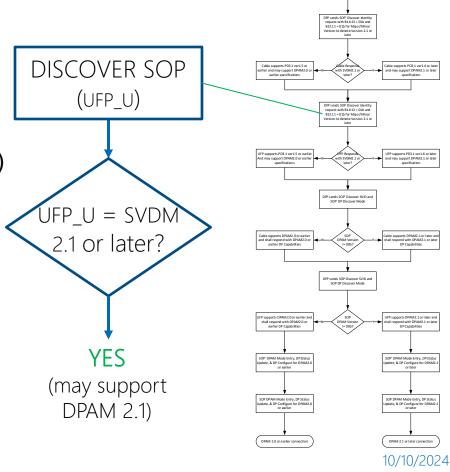

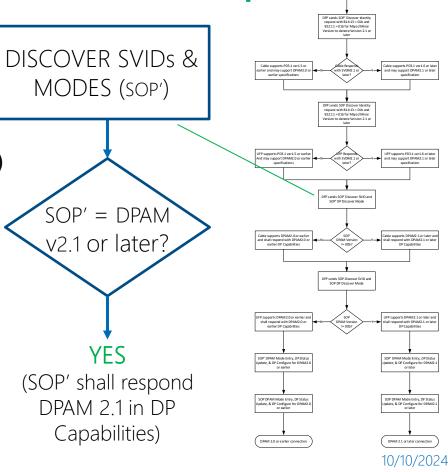

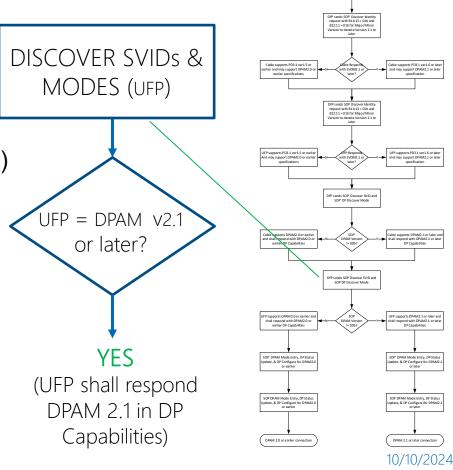

### **DPAM 2.1 Version Resolution**

### **Key Changes: DISCOVER MODE Response**

10/10/2024

### **VESA** Key Changes: DISCOVER MODE Response

#### Discover ID and Discover Modes (DP Capabilities) Response

will be identified by having a non-zero value in bits 31:24 of the VDO. The DFP U shall examine the list of modes returned until it finds 0s in bits 31:24 of the VDO and a non-zero value in bits 23:0 of the VDO (i.e., DisplayPort capabilities). The DFP U and UFP U shall use the corresponding offset (indexed from 1) as the Object Position in the Enter Mode, DisplayPort Configure, DisplayPort Status Undate. Attention, and Exit Mode commands.

SOP

#### DPAM2 0

| Table 5-5: DP Capabilities (VDO in the Responder Discover Modes VDM) |                                                                |                                                                                                                      |

|----------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Bit(s)                                                               | Description                                                    | Values <sup>a</sup>                                                                                                  |

| 1:0                                                                  | Port Capability                                                | 00b = RESERVED.                                                                                                      |

|                                                                      |                                                                | 01b = DP Sink device-capable (including DP Branch device).                                                           |

|                                                                      |                                                                | 10b = DP Source device-capable (including DP Branch device).                                                         |

|                                                                      |                                                                | 11b = Both DP Source and Sink device-capable.                                                                        |

| 5:2                                                                  | Signaling for Transport<br>of DisplayPort Protocol             | XXX1b = Supports DP Standard bit rates and electrical settings (shall always be set apart from diagnostic purposes). |

|                                                                      |                                                                | XX1Xb = RESERVED.                                                                                                    |

|                                                                      |                                                                | X1XXb = RESERVED.                                                                                                    |

|                                                                      |                                                                | 1XXXb = RESERVED.                                                                                                    |

| 6                                                                    | Receptacle Indication                                          | 0 = DP interface is presented on a USB-C plug.                                                                       |

|                                                                      |                                                                | 1 = DP interface is presented on a USB-C receptacle.                                                                 |

| 7                                                                    | USB 2.0 Signaling Not Used                                     | 0 = USB 2.0 may be needed on A6 – A7 –or– B6 – B7 while<br>in DisplayPort Configuration.                             |

|                                                                      |                                                                | 1 = USB 2.0 is not needed on A6 – A7 –or– B6 – B7 while<br>in DisplayPort Configuration.                             |

| 15:8                                                                 | DP Source Device Pin                                           | 00000000b = DP Source device pin assignments are not supported.                                                      |

|                                                                      | Assignments Supported<br>(reported by a DP Source device       | XXXXXXX1b = RESERVED.                                                                                                |

|                                                                      | receptacle or DP Sink device                                   | XXXXXX1Xb = RESERVED.                                                                                                |

|                                                                      | (direct-attach) plug)                                          | XXXXX1XXb = Pin Assignment C is supported.b                                                                          |

|                                                                      |                                                                | XXXX1XXXb = Pin Assignment D is supported. c d                                                                       |

|                                                                      |                                                                | XXX1XXXXb = Pin Assignment E is supported.*                                                                          |

|                                                                      |                                                                | XX1XXXXXb = RESERVED.                                                                                                |

|                                                                      |                                                                | X1XXXXXXb = RESERVED.                                                                                                |

|                                                                      |                                                                | 1XXXXXXXb = RESERVED.                                                                                                |

| 23:16                                                                | DP Sink Device Pin Assignments                                 | 00000000b = DP Sink device pin assignments are not supported                                                         |

|                                                                      | Supported (reported by a DP Sink                               | XXXXXXX1b = RESERVED.                                                                                                |

|                                                                      | device receptacle or DP Source<br>device (direct-attach) plug) | XXXXXXIXb = RESERVED.                                                                                                |

|                                                                      | 7. 0                                                           | XXXXX1XXb = Pin Assignment C is supported f                                                                          |

|                                                                      |                                                                | XXXX1XXXb = Pin Assignment D is supports. c g                                                                        |

|                                                                      |                                                                | XXX1XXXXb = Pin Assignment E is properted.h                                                                          |

|                                                                      |                                                                | XX1XXXXXb = RESERVED.                                                                                                |

|                                                                      |                                                                | X1XXXXXXb = RESERVE                                                                                                  |

|                                                                      |                                                                | 1XXXXXXXb = RESE D.                                                                                                  |

DPAM2.1

Signaling for Transport of DisplayPort Protocol apart from diagnostic pur XXIXb = RESERVE Recentacle Indication n DisplayPort Configuration XX1XXXXXb = RESERVE VI YYYYYYh = RESERV VVVVVVV - PESER DP Sink Device Pin XXXXXXXIb=F (reported by a DP Sink device receptacle CCCCCCCb = RESERVED 00b = Version 2.0 or earlier.

SOP'

#### DPAM2 0

|        | SOP' Cable DP Capabilities (DPAM2.0)      |            |  |  |

|--------|-------------------------------------------|------------|--|--|

| Bits   | Field                                     | CTS Value  |  |  |

| B31-24 | Reserved                                  | 0000 0000b |  |  |

| B23-16 | DP Sink Device Pin Assignment Supported   | 0000 1100b |  |  |

| B15-8  | DP Source Device Pin Assignment Supported | 0000 1100b |  |  |

| B7-6   | Reserved                                  | d00        |  |  |

| B5-2   | Signal for Transport of DP Protocol       | 0001b      |  |  |

| B1-0   | Reserved                                  | 00b        |  |  |

|        |                                           |            |  |  |

DPAM2 1

| Bit(s)             | Description                                 | Values                                                                                                      |

|--------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 1:0                | RESERVED                                    | RESERVED (always 00b).                                                                                      |

| 5:2                | Signaling for<br>Transport of               | XXX1b = Supports All defined DP bit rates up to HBR3.<br>XX1Xb = Supports DP bit rate UHBR10.               |

|                    | DisplayPort Protocol <sup>b</sup>           | X1XXb = Supports DP bit rate of UHBR20 (e.g., 0111b supports all DP bit ra<br>including UHBR10 and UHBR20). |

|                    |                                             | All other values are RESERVED for higher bit rates. <sup>c</sup>                                            |

| 7:6                | RESERVED                                    | RESERVED (always 00b).                                                                                      |

| 15:8               | DP Source Device Pin                        | 0Ch = Pin Assignments C and D are supported.                                                                |

|                    | Assignments Supported                       | 10h = USB-C and DP connector Pin Assignment E is supported.                                                 |

|                    |                                             | All other values are RESERVED.                                                                              |

| 23:16              | DP Sink Device Pin<br>Assignments Supported | 0Ch = Pin Assignments C and D are supported<br>(USB-C-to-USB-C cable).                                      |

|                    |                                             | 10h = USB-C and DP connector Pin Assignment E is supported.                                                 |

|                    |                                             | All other values are RESERVED.                                                                              |

| 25:24              | RESERVED                                    | RESERVED (always 00b).                                                                                      |

| 26 <sup>8</sup>    | UHBR13.5                                    | 0 = UHBR13.5 is not supported.                                                                              |

|                    |                                             | 1 = UHBR13.5 is supported.*                                                                                 |

| 27                 | RESERVED                                    | RESERVED (always 0).                                                                                        |

| 29:28 <sup>d</sup> | Active Component                            | 00b = Passave.                                                                                              |

|                    |                                             | 01b = Active re-timer.                                                                                      |

|                    |                                             | 10b = Active re-driver.                                                                                     |

|                    |                                             | 11b = Optical.                                                                                              |

| 31:30              | DPAM Version                                | 00b = Original version.                                                                                     |

|                    |                                             | 01b = Version 1.                                                                                            |

Discover Modes Response from UFP

Discover Modes Response from Cable

### **VESA** Structured VDM Version

Structured VDM

Version (Minor)a

Structured VDM Version (Major)<sup>a</sup>

SVDM Version Revised in Power Delivery Spec (Revision 1.3; Version 1.6)

12:11

Adds Major & Minor "VDM" version fields

| Tabl | e 5-4: | SVDM | Header |

|------|--------|------|--------|

|------|--------|------|--------|

| VOR                                                        | Bit(s) | Description                                                                                                             | Values                                                                        |

|------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| ver                                                        | 4:0    | Command                                                                                                                 | 0h = RESERVED, shall not be used.                                             |

|                                                            |        |                                                                                                                         | lh = USB PD Discover Identity.                                                |

| reion 16)                                                  |        |                                                                                                                         | 2h = USB PD Discover SVIDs.                                                   |

| rsion 1.6)                                                 |        |                                                                                                                         | 3h = USB PD Discover Modes.                                                   |

|                                                            |        |                                                                                                                         | 4h = Enter Mode.                                                              |

| fields                                                     |        |                                                                                                                         | 5h = Exit Mode.                                                               |

|                                                            |        |                                                                                                                         | 6h = USB PD Attention.                                                        |

|                                                            |        |                                                                                                                         | 7h - Fh = RESERVED, shall not be used.                                        |

|                                                            |        |                                                                                                                         | 10h = DisplayPort Status Update.                                              |

|                                                            |        |                                                                                                                         | 11h = DisplayPort Configure.                                                  |

|                                                            |        |                                                                                                                         | 12h - 1Fh = RESERVED for DP_SID use.                                          |

| Version number (Minor) of the SVDM (not the USB PD version |        | B PD version                                                                                                            | RESERVED (always 0).                                                          |

| number).                                                   |        |                                                                                                                         | 00b = REQ (Request from Initiator Port).                                      |

| 00b = Version 2.0 or earlier                               |        |                                                                                                                         | 01b = ACK (USB PD Responder ACK response).                                    |

| 01b = Version 2.1                                          |        |                                                                                                                         | 10b = NAK (USB PD Responder NAK response).                                    |

| All other values are I ESERVED.                            | _      | 11b = BUSY (USB PD Responder BUSY response).                                                                            |                                                                               |

|                                                            | D DDi  | For Enter Mode Command requests/responses, Exit Mode Command requests/responses, and USB PD Attention Command requests: |                                                                               |

| Version number (Major) of the SVDM (not the USB PD version |        |                                                                                                                         | 000b = RESERVED.                                                              |

| number).                                                   |        |                                                                                                                         | 001b - 110b = Index into the list of Vendor Defined Objects                   |

| 00b = Version 2.0 or earlier                               |        |                                                                                                                         | (VDOs) to identify the needed Mode VDO.                                       |

| 00b = Version 2.0 or earlier.                              |        |                                                                                                                         | 111b = Exit all Active Modes (equivalent of a power-on reset).                |

| 01b = Version 2.x. (x indicates SVDM                       | n)     | Shall only be used with an Exit Mode Command request.                                                                   |                                                                               |

| All other values are RESERVED.                             |        |                                                                                                                         | For USB PD Discover Identity, Discover SVIDs, and Discover                    |

| All other values are RESERVED.                             |        |                                                                                                                         | Modes Command requests/responses:                                             |

|                                                            |        |                                                                                                                         | • 000b.                                                                       |

|                                                            |        |                                                                                                                         | <ul> <li>001b – 111b = RESERVED.</li> </ul>                                   |

|                                                            | 12:1   | Structured VDM Version<br>(Minor)*                                                                                      | Version number (Minor) of the SVDM (not the <i>USB PD</i> version<br>number). |

| 2.0                                                        | 1      | (Mimor)                                                                                                                 | number).<br>00b = Version 2.0 or earlier                                      |

| <b>∠()</b>                                                 |        |                                                                                                                         | 01b = Version 2.1                                                             |

| ۷.0                                                        | 1410   | C. ITTPLET                                                                                                              | All other values are RESERVED.                                                |

- SVDM Minor: 2.0 = DP Alt mode 2.0

- SVDM Minor: 2.1 = DP Alt mode 2.1

|   |       |                                                | For USB PD Discover Identity, Discover SVIDs, and Discover Modes Command requests/responses:                                                                                                     |

|---|-------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |       |                                                | <ul> <li>000b.</li> <li>001b – 111b = RESERVED.</li> </ul>                                                                                                                                       |

|   | 12:13 | Structured VDM Version<br>(Minor)*             | Version number (Minor) of the SVDM (not the USB PD version number).  00b = Version 2.0 or earlier 01b = Version 2.1 All other values are RESERVED.                                               |

|   | 14:13 | Structured VDM Version<br>(Major) <sup>a</sup> | Version number (Major) of the SVDM (not the USB PD version<br>number).<br>00b = Version 2.0 or earlier.<br>01b = Version 2.x. (x indicates SVDM minor version)<br>All other values are RESERVED. |

| ľ | 15    | VDM Type                                       | 1 = SVDM.                                                                                                                                                                                        |

|   | 31:16 | Standard or Vendor ID<br>(SVID)                | Base SID (for a <i>USB PD Discover SVIDs</i> Command request) or DP_SID, a 16-bit unsigned integer, assigned by the USB-IF.                                                                      |

| - |       | •                                              | •                                                                                                                                                                                                |

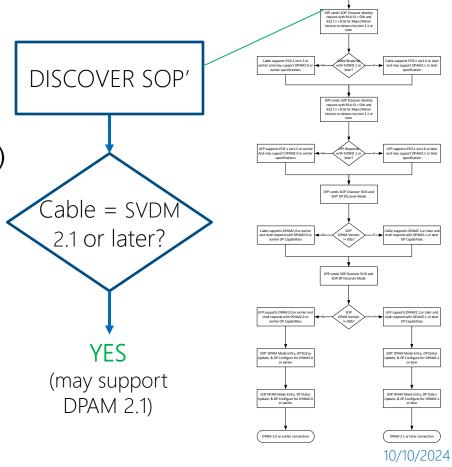

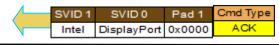

## **VESA** SVDM Version Resolution Example

SVDM Version resolution

DISCOVER IDENTITY (SOP'/ UFP)

- DISCOVER SVIDs (SOP'/ UFP)

- DISCOVER MODES (SOP'/ UFP)

- ◆ DFP\_U sends Discover Modes IF response "SVDM version = 2.1" then use "DPAM 2.1"

- ◆ Else must use "DPAM 2.0"

- ENTER MODE (SOP'/ UFP)

- DP CONFIGURE (SOP'/ UFP)

## **VESA** SVDM Version Resolution Example

SVDM Version resolution

- DISCOVER IDENTITY (SOP'/ UFP)

- DISCOVER SVIDs (SOP'/ UFP)

- DISCOVER MODES (SOP'/ UFP)

- ◆ DFP\_U sends Discover Modes IF response "SVDM version = 2.1" then use "DPAM 2.1"

- ◆ Else must use "DPAM 2.0"

- ENTER MODE (SOP'/ UFP)

- DP CONFIGURE (SOP'/ UFP)

DFP DPAM Capable connectio

## **VESA** SVDM Version Resolution Example

SVDM Version resolution

DISCOVER IDENTITY (SOP'/ UFP)

- DISCOVER SVIDs (SOP'/ UFP)

- DISCOVER MODES (SOP'/ UFP)

- ◆ DFP\_U sends Discover Modes IF response "SVDM version = 2.1" then use "DPAM 2.1"

- ◆ Else must use "DPAM 2.0"

- ENTER MODE (SOP'/ UFP)

- DP CONFIGURE (SOP'/ UFP)

# **VESA** SVDM Version Resolution Example

SVDM Version resolution

DISCOVER IDENTITY (SOP'/ UFP)

- DISCOVER SVIDs (SOP'/ UFP)

- DISCOVER MODES (SOP'/ UFP)

- ◆ DFP\_U sends Discover Modes IF response "SVDM version = 2.1" then use "DPAM 2.1"

- ◆ Else must use "DPAM 2.0"

- ENTER MODE (SOP'/ UFP)

- ◆ DP CONFIGURE (SOP'/ UFP)

# **VESA** SVDM Version Resolution Example

SVDM Version resolution

- DISCOVER IDENTITY (SOP'/ UFP)

- DISCOVER SVIDs (SOP'/ UFP)

- DISCOVER MODES (SOP'/ UFP)

- ◆ DFP\_U sends Discover Modes IF response "SVDM version = 2.1" then use "DPAM 2.1"

- ♦ Else must use "DPAM 2.0"

- ENTER MODE (SOP'/ UFP)

- DP CONFIGURE (SOP'/ UFP)

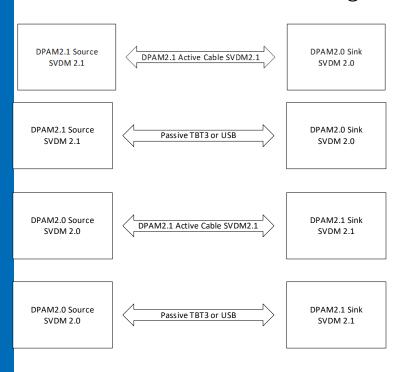

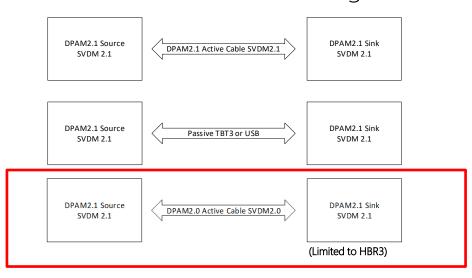

### **VESA DP Alt-Mode SVDM Resolution Scenarios**

#### DFP sends **DPAM2.0** DP Configure

#### DFP sends **DPAM2.1** DP Configure

Signaling for Transpor

DP Source Device Pin

(direct-attach) plug)

Assignments Supported

(reported by a DP Source device

receptacle or DP Sink device

DP Sink Device Pin Assign

device (direct-attach) plug)

Supported (reported by a DP Sink

device receptacle or DP Source

XXXXXXIXh = RESERVED

XX1XXXXXb = RESERVED

X1XXXXXXb = RESERVED

XXXXXXXX = RESERVED

XXXXXXXIb = RESERVED

XXXXXX1Xb = RESERVED

XX1XXXXXb = RESERVED.

X1XXXXXXh = RESERVED

0000000b = DP Sink device pin

XXXXX1XXb = Pin Assignment C is supported.

XXX1XXXXb = Pin Assignment E is supported.

XXXXX1XXb = Pin Assignment C is supported.

XXXX1XXXb = Pin Assignment D is supported.<sup>c</sup> 8

XXX1XXXXb = Pin Assignment E is supported.

XXXX1XXXb = Pin Assignment D is supported. c d

of DisplayPort Protocol

# VESA Key Field Changes: DISCOVER MODE Response

Active Component

29:28d

SOP DPAM2 1 DPAM2 0 Table 5-5: DP Capabilities (VDO in the Description Port Capability 01b = DP Sink device-capable (including D. OON = RESERVED 10b - DP Source device-capable (including 01b = DP Sink device-capable (including DP Branch device). 11b = Both DP Source and Sink device-ca 10b = DP Source device-capable (including DP Branch device) 11b = Both DP Source and Sink device-capable Signaling for Transport of DisplayPort Protocol XXX1b = Supports DP bit rates and e apart from diagnostic purposes). XXX1b = Supports DP Standard bit rates and electrical settings (shall YV1Vb = RESERVED always be set apart from diagnostic purposes X1XXb=RESERVED. XXXb = RESERVED X1XXb = RESERVED Receptacle Indication = DP interface is presen 1XXXb = RESERVED. = DP interface is present Creceptacle = DP interface is presented on a USB-C plug. USB 2.0 Signaling Not Used = DP interface is presented on a USB-C recentacle in DisplayPort Configurat = USB 2.0 may be needed on A6 - A7 -or- B6 - B7 while l = USB 2.0 is not needed in DisplayPort Configuration in DisplayPort Configu 1 = USB 2.0 is not needed on A6 - A7 -or- B6 - B7 while DP Source Device Pin 00000000b = DP So in DisplayPort Configuration Assignments Supported (reported by a DP Source VVVVVVV16 - PI 0000000b = DP Source device pin assignments are not sup-XXXXXXXIXb XXXXXXXIb = RESERVED DP Sink device ssignment C is supported.

(direct-attach) plug

23:16 DP Sink Device Pin

29:24 RESERVED

31:30 DPAM Version<sup>i</sup>

(reported by

or DP Source device (direct-attach) plug)

a DP Sink device receptacle

XXXIXXX

= RESERVED

XXXX1XXb = Pin Assignment C is supported

OCX1XXXXb = Pin Assignment E is supported.

CXXX1XXXb = Pin Assignment D is supported.c1

Th = RESERVED

VVI - PESERVED

XXXX1b = RESERVED

XXXX1Xb - RESERVED.

VY1YYYYYh = RESERVED

X1XXXXXXXb = RESERVED

XXXXXXXb = RESERVED

RESERVED (always 00h)

00b = Version 2.0 or earlier

XX1XXX

10b = Active re-driver. 11b = Optical. Signaling for XXX1b = Supports all defined DP bit rates up to HBR3 Transport of XX1Xb = Supports DP bit rate UHBR10.DisplayPort Protocolb X1XXb = Supports DP bit rate of UHBR20 (e.g., 0111b supports all DP bit rates, including UHBR10 and UHBR20). **UHBR13.5** 0 = UHBR13.5 is not supported. 1 = UHBR13.5 is supported.e DPAM RESERVED DPAM2.0 Transport of XX1Xb = Supports DP bit rate UHBR1 V1VVb - Supports DR his cate of CURRY 20 Ja including UHBR10 and UHBR20 SOP' Cable DP Capabilities (DPAM2.0) All other values are RESERVED for higher bit rates PECEPTED (shows 00h EPTED CTS Val Bits Field 15:8 0Ch = Pin Assignments C and D are supp 10h = USB-C and DP connector Pin Assignment E is supported B31-24 Reserved oooo oooo All other values are PESERVED 0Ch = Pin Assignments C and D are suppo B23-16 DP Sink Device Pin Assignment Supported 0000 1100b (USB-C-to-USB-C cable) 10h = USB-C and DP connector Pin Assignment E is supported B15-8 DP Source Device Pin Assignment Supported 0000 1100b All other values are RESERVED B7-6 Reserved 00hRESERVE RESERVED (always 00b) 0 = UHBR13.5 is not supporte-B5-2 Signal for Transport of DP Protocol 0001b = UHBR13.5 is supported.6 RESERVED (always 0 B1-0 Reserved 00b 01b = Active re-times 10b = Active re-drive 11b = Optical Discover Modes Response from Cable

00b = Passive.

01b = Active re-timer.

Discover Modes Response from UFP

10/10/2024

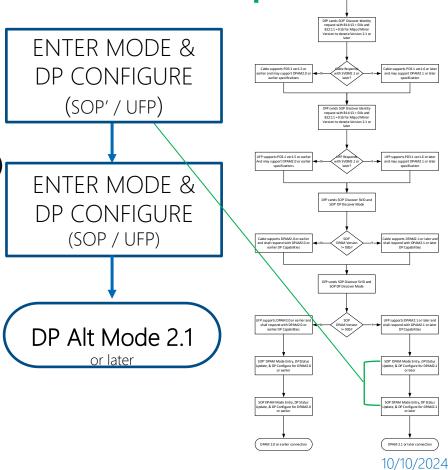

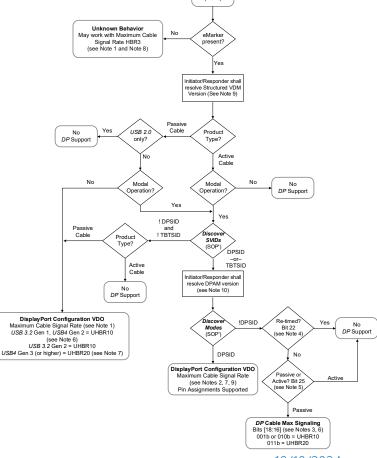

# DP Alt Mode 2.1 Configuration with Active Cable

- DFP\_U Must send ENTER

MODE to the Cable

- C-to-DP Adapters: should support "reversible" operation

- if not, visually indicate which direction they support

- Active Type-C Cables must support one bidirectional USB 3.2 link

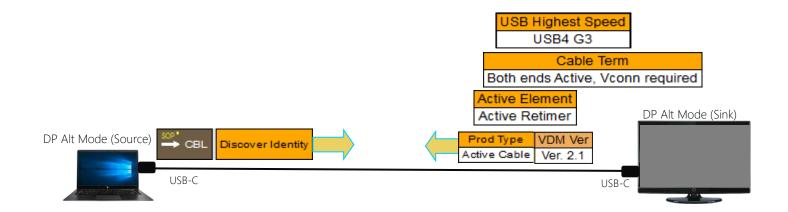

#### DFP Sends Discover Identity to the Cable (SOP')

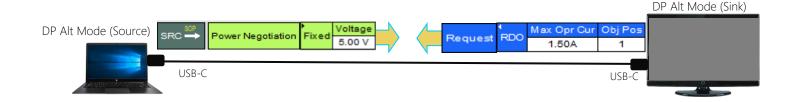

#### **DFP Negotiates Initial Power Delivery Contract**

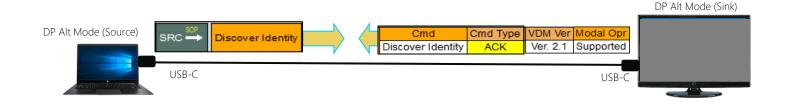

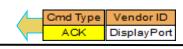

### VESA DFP Sends Discover Identity to the Sink (SOP)

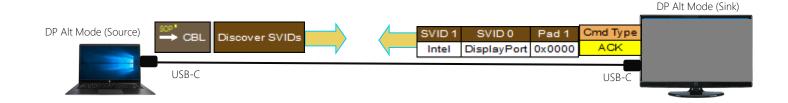

#### **VESA** DFP Sends Discover SVIDs to the Cable (SOP')

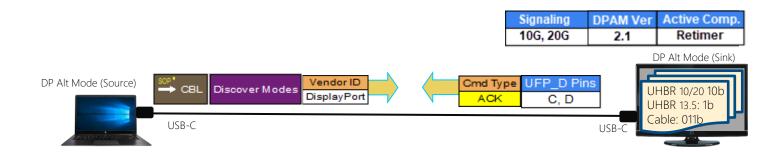

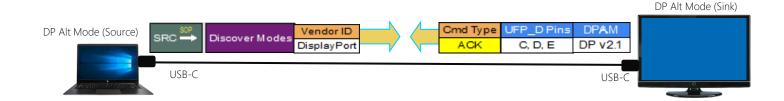

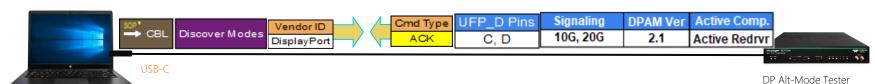

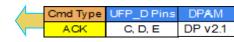

#### **VESA** DFP Sends Discover Modes to the Cable (SOP')

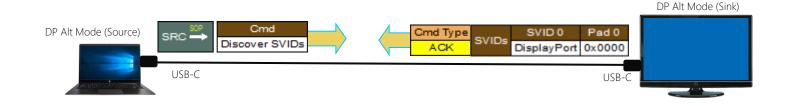

#### **VESA** DFP Sends Discover SVIDs to the Sink (SOP)

# **VESA** DFP Sends Discover Modes to the Sink (SOP)

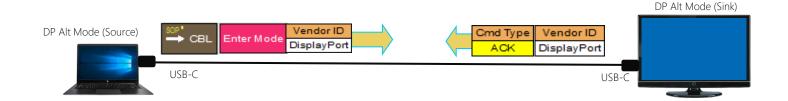

# **VESA** DFP Sends Enter Mode to the Cable (SOP')

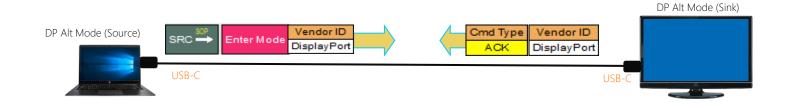

#### VESA DFP Sends Enter Mode to the Sink (SOP)

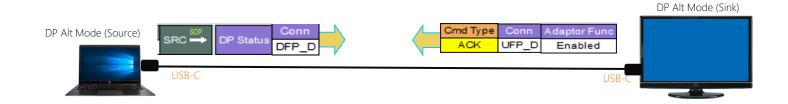

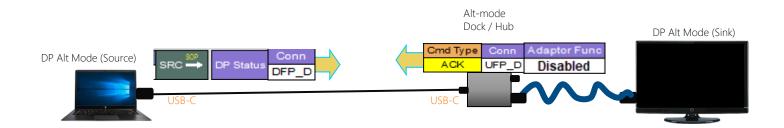

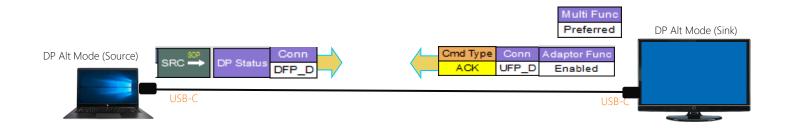

#### **VESA** DFP Sends DP Status to the Sink (SOP)

#### **VESA** DFP Sends DP Status to the Sink (SOP)

#### **VESA** DFP Sends DP Status to the Sink (SOP)

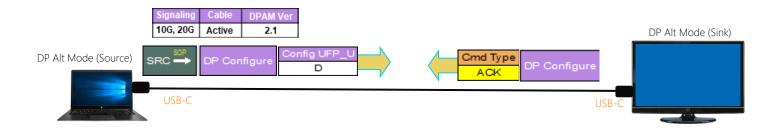

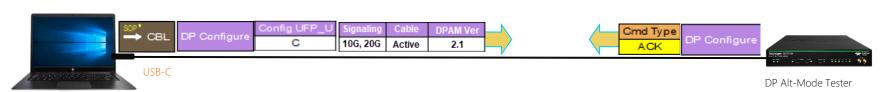

#### **VESA** DFP Sends DP Configure to the Cable (SOP')

#### VESA DFP Sends DP Configure to the Sink (SOP)

#### **VESA** UFP Sends Attention Message to the DFP

### **VESA** UFP Sends Attention Message to the DFP

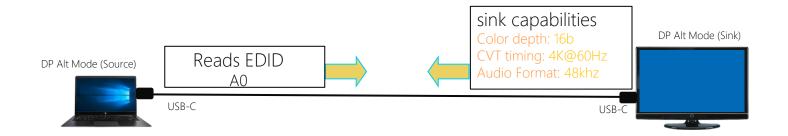

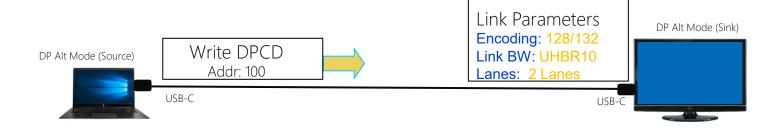

## **VESA** Link Training: Read DisplayID or legacy EDID

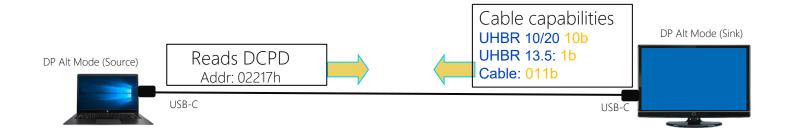

# **VESA** Link Training: Read Cable Capabilities

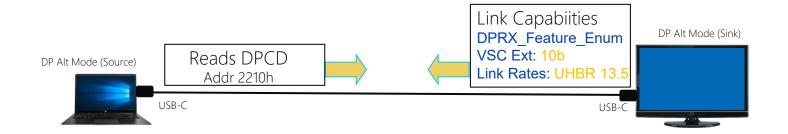

# **VESA** Link Training: Read Link Capabilities

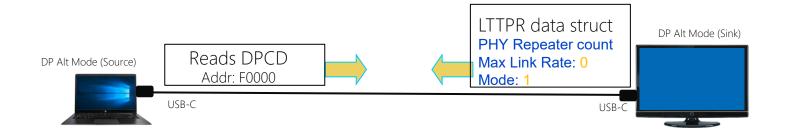

# **VESA** Link Training: Read LTTPR Data

# **VESA** Link Training: Lanes & Link Bandwidth Set

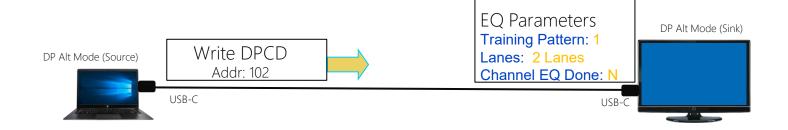

# **VESA** Link Training: Equalization & Clock Domain Switch

### **VESA** Link Training: Equalization & Clock Domain Switch

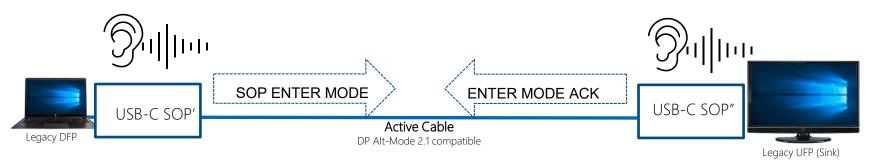

# VESA DP 2.1 Active Cable "Snoop" mode

- **Special Situation**: Legacy DP\_Sources that do not send ENTER MODE to the cable:

- **DP Alt Mode 2.1** Active cables are required to snoop SOP commands and silently perform the same on SOP' & SOP" for:

- ENTER MODE

- CONFIGURE

- EXIT MODE

# DP Alt-Mode v2.1a Compliance Test Specification

# VESA DP Alt Mode v2.1 Compilance Test Specification

#### Contents

- Ch:3 Physical Layer

- Ch:4 Cables

- Ch:5 Type-C-to-DP Plug Connector

- Ch:6 DP Alt Mode Protocol Converter

- Ch:7 DP Alt Mode Type-C Source

- Ch:8 DP Alt Mode Type-C Sink:

- Ch:9 AUX and HPD

- Ch:10 Discovery and USB PD

- Ch:11 VBUS and VCONN

Ouantumdata M42de DP 2.1 Compliance Tester

Voyager M310e USB-C Compliance Tester

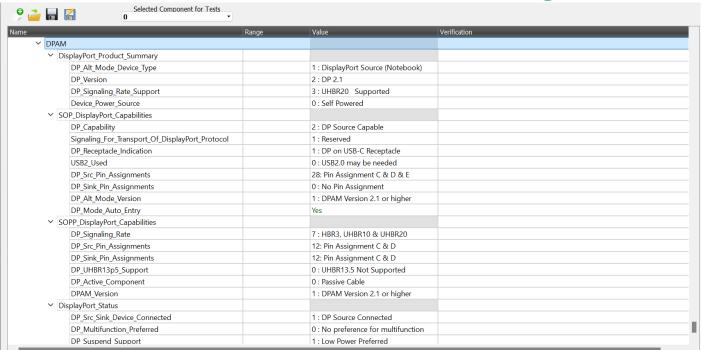

#### **DP Alt Mode VIF**

- Utilizes USB.org VIF: Optional Content fields

- Allows efficient testing of DPAM devices

- Download latest revision: <u>www.VESA.org</u>

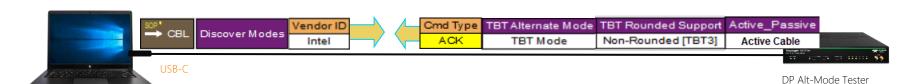

#### **VESA** DP Alt-Mode 2.1 Cable Discovery Tests (for DFPs)

Verify UUT identifies cable speed, type, DPAM ver w/ SOP DP CONFIGURE message

| Test    | Description                                                      |

|---------|------------------------------------------------------------------|

| 10.3.3  | Alt Mode Entry with USB Type-C to USB Type-C Passive non-emarked |

| 10.3.4  | Alt Mode Entry with USB Type-C to USB Type-C Passive TBT3 cable  |

| 10.3.5  | Alt Mode Entry with Type-C to Type-C Passive USB4 Gen3 cable     |

| 10.3.6  | Alt Mode Entry with Type-C to Type-C Active LRD DP2.0 cable      |

| 10.3.7  | Alt Mode Entry with Type-C to Type-C Active Retimer DP2.0 cable  |

| 10.3.8  | Alt Mode Entry with Type-C to Type-C Active Redriver DP2.1 cable |

| 10.3.9  | Alt Mode Entry with Type-C to Type-C Active Non - DP2.1/0 cable  |

| 10.3.10 | Alt Mode Entry with Type-C to Type-C USB2.0 Only cable           |

| 10.3.11 | Alt Mode Entry with Type-C to DP2.1 cable                        |

#### VESA DP Alt-Mode 2.1 Cable Discovery Tests (for DFPs)

Verify UUT identifies cable speed, type, DPAM ver w/ SOP DP CONFIGURE message

| Test    | Description                                                      |

|---------|------------------------------------------------------------------|

| 10.3.3  | Alt Mode Entry with USB Type-C to USB Type-C Passive non-emarked |

| 10.3.4  | Alt Mode Entry with USB Type-C to USB Type-C Passive TBT3 cable  |

| 10.3.5  | Alt Mode Entry with Type-C to Type-C Passive USB4 Gen3 cable     |

| 10.3.6  | Alt Mode Entry with Type-C to Type-C Active LRD DP2.0 cable      |

| 10.3.7  | Alt Mode Entry with Type-C to Type-C Active Retimer DP2.0 cable  |

| 10.3.8  | Alt Mode Entry with Type-C to Type-C Active Redriver DP2.1 cable |

| 10.3.9  | Alt Mode Entry with Type-C to Type-C Active Non - DP2.1/0 cable  |

| 10.3.10 | Alt Mode Entry with Type-C to Type-C USB2.0 Only cable           |

| 10.3.11 | Alt Mode Entry with Type-C to DP2.1 cable                        |

DP Alt-Mode Tester

#### DP Alt-Mode 2.1 Cable Discovery Tests (for DFPs)

Verify UUT identifies cable speed, type, DPAM ver w/ SOP DP CONFIGURE message

| Test    | Description                                                      |

|---------|------------------------------------------------------------------|

| 10.3.3  | Alt Mode Entry with USB Type-C to USB Type-C Passive non-emarked |

| 10.3.4  | Alt Mode Entry with USB Type-C to USB Type-C Passive TBT3 cable  |

| 10.3.5  | Alt Mode Entry with Type-C to Type-C Passive USB4 Gen3 cable     |

| 10.3.6  | Alt Mode Entry with Type-C to Type-C Active LRD DP2.0 cable      |

| 10.3.7  | Alt Mode Entry with Type-C to Type-C Active Retimer DP2.0 cable  |

| 10.3.8  | Alt Mode Entry with Type-C to Type-C Active Redriver DP2.1 cable |

| 10.3.9  | Alt Mode Entry with Type-C to Type-C Active Non - DP2.1/0 cable  |

| 10.3.10 | Alt Mode Entry with Type-C to Type-C USB 2.0 Only cable          |

| 10.3.11 | Alt Mode Entry with Type-C to DP2.1 cable                        |

DP Alt Mode (Source)

DP Alt-Mode Tester

Verify UUT identifies cable speed, type, DPAM ver w/ SOP DP CONFIGURE message

| Test    | Description                                                      |

|---------|------------------------------------------------------------------|

| 10.3.3  | Alt Mode Entry with USB Type-C to USB Type-C Passive non-emarked |

| 10.3.4  | Alt Mode Entry with USB Type-C to USB Type-C Passive TBT3 cable  |

| 10.3.5  | Alt Mode Entry with Type-C to Type-C Passive USB4 Gen3 cable     |

| 10.3.6  | Alt Mode Entry with Type-C to Type-C Active LRD DP2.0 cable      |

| 10.3.7  | Alt Mode Entry with Type-C to Type-C Active Retimer DP2.0 cable  |

| 10.3.8  | Alt Mode Entry with Type-C to Type-C Active Redriver DP2.1 cable |

| 10.3.9  | Alt Mode Entry with Type-C to Type-C Active Non - DP2.1/0 cable  |

| 10.3.10 | Alt Mode Entry with Type-C to Type-C USB 2.0 Only cable          |

| 10.3.11 | Alt Mode Entry with Type-C to DP2.1 cable                        |

DP Alt Mode (Source)

Verify UUT identifies cable speed, type, DPAM ver w/ SOP DP CONFIGURE message

| Test    | Description                                                      |

|---------|------------------------------------------------------------------|

| 10.3.3  | Alt Mode Entry with USB Type-C to USB Type-C Passive non-emarked |

| 10.3.4  | Alt Mode Entry with USB Type-C to USB Type-C Passive TBT3 cable  |

| 10.3.5  | Alt Mode Entry with Type-C to Type-C Passive USB4 Gen3 cable     |

| 10.3.6  | Alt Mode Entry with Type-C to Type-C Active LRD DP2.0 cable      |

| 10.3.7  | Alt Mode Entry with Type-C to Type-C Active Retimer DP2.0 cable  |

| 10.3.8  | Alt Mode Entry with Type-C to Type-C Active Redriver DP2.1 cable |

| 10.3.9  | Alt Mode Entry with Type-C to Type-C Active Non - DP2.1/0 cable  |

| 10.3.10 | Alt Mode Entry with Type-C to Type-C USB 2.0 Only cable          |

| 10.3.11 | Alt Mode Entry with Type-C to DP2.1 cable                        |

DP Alt Mode (Source)

DP Alt Mode (Source)

Verify UUT identifies cable speed, type, DPAM ver w/ SOP DP CONFIGURE message

| Test    | Description                                                      |

|---------|------------------------------------------------------------------|

| 10.3.3  | Alt Mode Entry with USB Type-C to USB Type-C Passive non-emarked |

| 10.3.4  | Alt Mode Entry with USB Type-C to USB Type-C Passive TBT3 cable  |

| 10.3.5  | Alt Mode Entry with Type-C to Type-C Passive USB4 Gen3 cable     |

| 10.3.6  | Alt Mode Entry with Type-C to Type-C Active LRD DP2.0 cable      |

| 10.3.7  | Alt Mode Entry with Type-C to Type-C Active Retimer DP2.0 cable  |

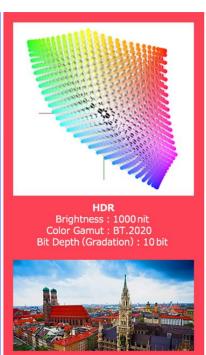

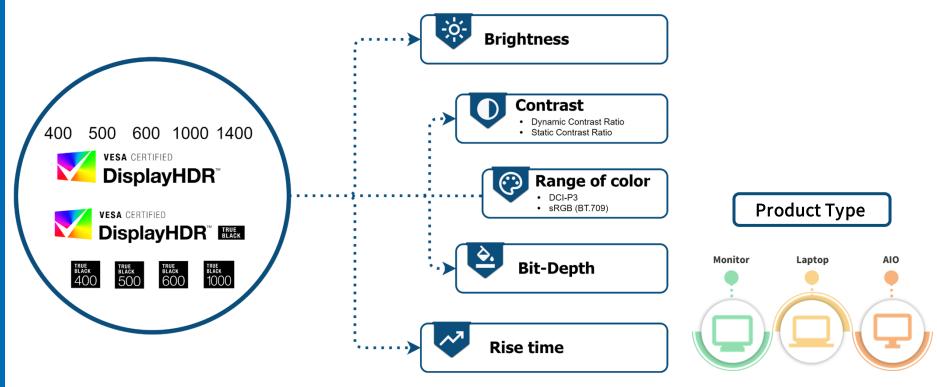

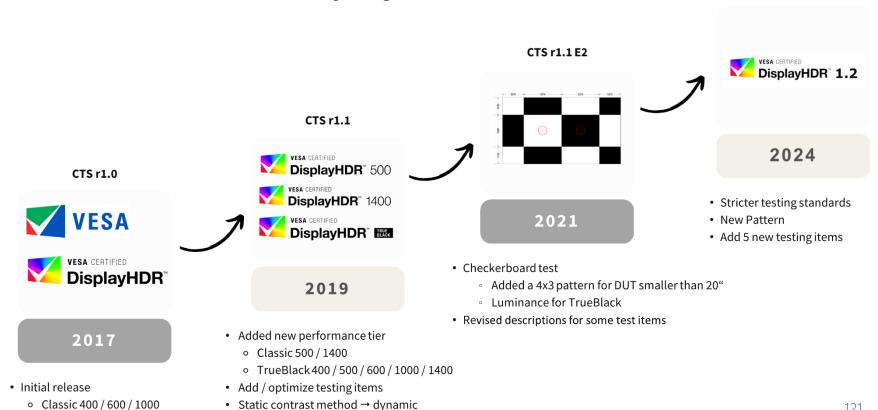

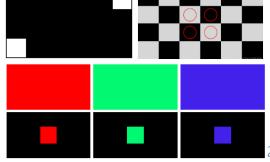

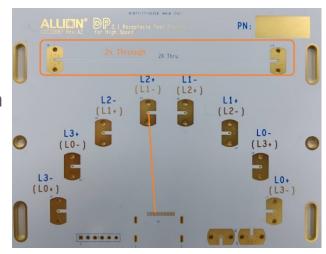

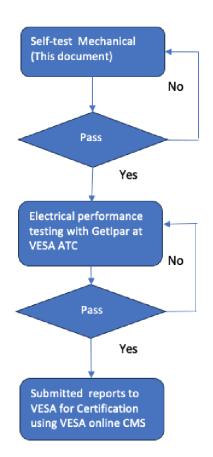

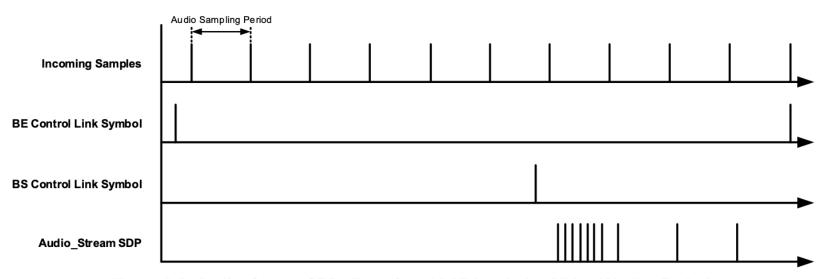

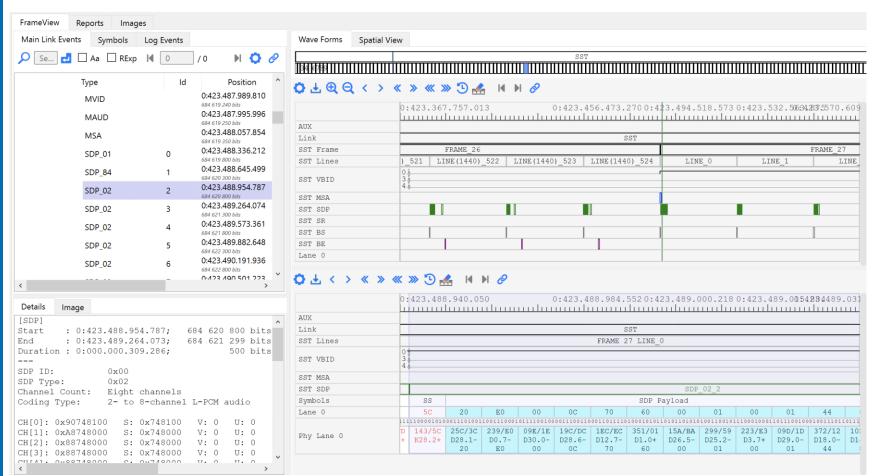

| 10.3.8  | Alt Mode Entry with Type-C to Type-C Active Redriver DP2.1 cable |